I am a 4th-year Ph.D. candidate at Peking University, advised by Prof. Yibo Lin. My research interests include data structures, algorithm design and GPU acceleration for combinatorial optimization problems in physical design automation.

Currently, I hold broad interest in topics like signoff timing analysis, power analysis, logic simulation, and performance-driven backend EDA tasks.

My Chinese name is 郭资政.

Interests

- Data Structure and Algorithms

- GPU Acceleration using CUDA

- Reinforcement Learning

Education

-

BSc in Computer Science, 2018-2022

Peking University

-

PhD Student, 2022-

Peking University

Recent Publications

(2026).

Disentangled Differentiable Timing-Power Co-Optimization with Quad-Gradient Gate Sizing.

63rd ACM/IEEE Design Automation Conference (DAC) 2026.

(2026).

Provably Optimal Planar Pareto Nearest Neighbor Search with Double Monotone Chains.

2026 IEEE/ACM Design, Automation and Test in Europe (DATE).

(2026).

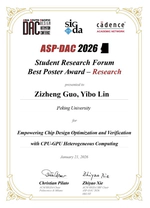

HeteroSTA: A CPU-GPU Heterogeneous Static Timing Analysis Engine with Holistic Industrial Design Support.

IEEE/ACM Asia and South Pacific Design Automation Conference (ASPDAC) 2026.

(2026).

GAP-LA: GPU-Accelerated Performance-Driven Layer Assignment.

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems.

(2026).

HeteroLatch: A CPU-GPU Heterogeneous Latch-Aware Timing Analysis Engine.

IEEE/ACM Asia and South Pacific Design Automation Conference (ASPDAC) 2026.